Содержание

- Компиляция проекта

- Унифицированная модель данных

- Изучение связности в панели Navigator

- Верификация компонентов

- Настройка верификации

- Графические проверки

- Проверки связности

- Осмысление сообщений и поиск ошибок

- Исправление предупреждений и ошибок

- Использование директивы No ERC

- Исправление предупреждений и ошибок

- Подробнее об ошибках компилятора

Полное содержание

Главная страница: Подробнее о схемах

Компиляция проекта

Что означает компиляция проекта? Зачем необходимо компилировать проект? Почему система не может просто отслеживать связность схемы в процессе ее создания?

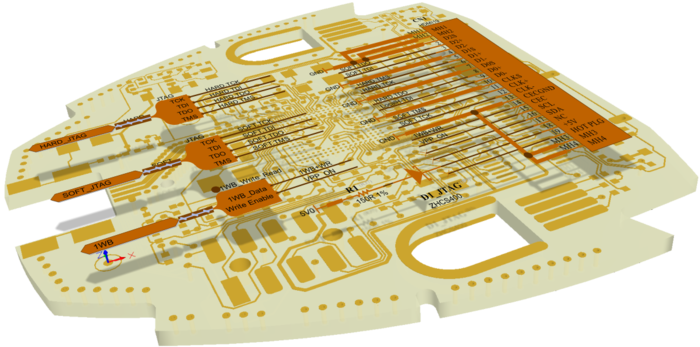

Система управляет связанными данными на схеме и на плате.

В конечном счете, системе необходимо построить модель связности всего проекта, как для схемы, так и для платы. Если делать это динамически, т.е. с постоянным отслеживанием связности, то данные о компонентах и связях всего проекта должны быть доступными, когда проект открыт, что потребует хранения всех этих данных в одном файле. Хранение всех данных всех листов большой многоканальной схемы в одном файле возможно, но, по ряду причин, это не является лучшим подходом.

Если проводить аналогию с разработкой программного обеспечения, то весь исходный код приложения хранился бы в одном файле, и программирование велось бы в среде разработки, которая компилировала бы приложение повторно при каждом изменении файла. Конечно, такой подход не устраивает программистов. Средства разработки позволяют разделить исходный код на множество файлов и разграничить процессы создания, анализа и компиляции. Это позволяет разработчику беспрепятственно создавать и редактировать исходный код, используя нужную структуру файлов. Они компилируют исходники для создания работающего кода только тогда, когда, по их мнению, это необходимо.

Благодаря подобному подходу, инженер-схемотехник может свободно размещать, связывать, перемещать, переименовывать, добавлять и удалять содержимое своего проекта. Когда проект, по мнению инженера, готов, он компилирует его, с его проверкой и построением внутренней модели связности. Такой подход также поддерживает хранение листов схем в отдельных файлах, что позволяет легко переносить данные из предыдущих проектов и осуществлять одновременную совместную работу множества инженеров над одним проектом.

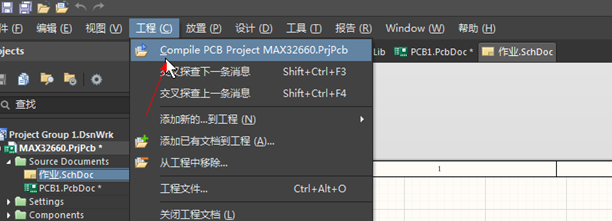

Когда проект готов к компиляции, выберите команду Compile PCB Project в меню Project.

Система:

- Строит список цепей для каждого листа схемы.

- Создает связность между листами.

- Строит унифицированную модель данных.

- Анализирует весь проект на графические и электрические ошибки.

Благодаря этому подходу, редактор схем становится интеллектуальным средством черчения, а не просто инструментом для определения связей. Когда вы соединяете два вывода с помощью провода, вы, по сути, фиксируете свой инженерный замысел, а не создаете цепь. Цепь не будет создана до момента компиляции проекта, и этот процесс управляется алгоритмами за пределами редактора схем. Как упоминалось ранее, существует ряд преимуществ этого подхода, самым большим из которых является то, что скомпилированная модель проекта находится вне редактора схем и редактора плат. Скомпилированная модель называется унифицированной моделью данных (Unified Data Model – UDM). Эта модель включает в себя подробное описание каждого компонента в проекте и его связь с другими компонентами.

Чтобы узнать подробнее о создании связности, перейдите на страницу Создание связности.

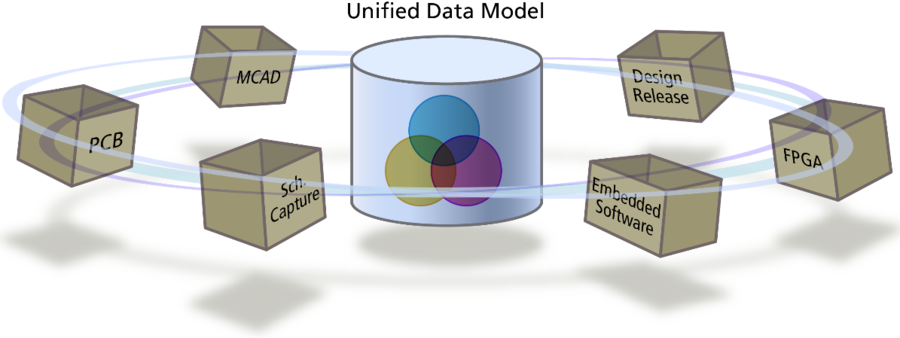

Унифицированная модель данных

В основе системы лежит унифицированная модель данных (Unified Data Model – UDM). При компиляции проекта происходит создание единой связанной модели, которая занимает центральное место в процессе проектирования. Данные этой модели затем можно открывать и изменять с помощью различных редакторов и служб системы. Вместо того, чтобы хранить данные каждого аспекта проектирования по отдельности, модель UDM структурирована для хранения всей информации о проекте, в том числе о компонентах и связи между ними.

Унифицированная модель данных делает данные о проекте доступными для всех редакторов, что позволяет использовать такие возможности продвинутого проектирования, как многоканальное проектирование и варианты.

Итак, как же взаимодействовать с унифицированной моделью данных, чтобы, например, отследить цепь в проекте? Это осуществляется через панель Navigator.

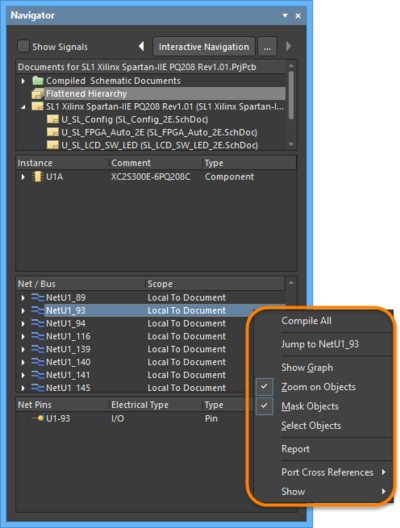

Изучение связности в панели Navigator

Справочная страница: Панель Navigator

Если проект большой и разбит на множество листов, может быть сложно отследить цепь и проверить связность проекта, просто взглянув на схему. Чтобы упростить этот процесс, используется панель Navigator. Панель отображает весь скомпилированный проект, поэтому она будет пустой, пока вы не скомпилируете проект (Project » Compile PCB Project). Панель Navigator можно открыть, нажав кнопку Panels в нижней правой части приложения и выбрав Navigator.

Чтобы использовать панель:

- Задайте поведение просмотра, нажав кнопку

в верхней части панели – будет открыта страница System — Navigation диалогового окна Preferences, где вы сможете задать предпочитаемый метод подсветки (настройки области Highlight Methods). Либо щелкните ПКМ по интересующему объекту в панели и используйте команды контекстного меню для настройки поведения навигации.

- Задайте область просмотра в первой области панели. Для просмотра всего проекта выберите

Flattened Hierarchy. - Щелкните мышью по компоненту в области Instance панели, чтобы перейти к этому компоненту, или разверните компонент, чтобы найти вывод и перейти к нему.

- Щелкните мышью по цепи или шине в области Net / Bus, чтобы перейти к этой цепи или шине, или разверните цепь или шину, чтобы найти вывод и перейти к нему.

Щелкните по компоненту или цепи в панели Navigator, чтобы найти этот компонент или цепь и отследить связность в проекте. Щелкните ПКМ, чтобы показать варианты отображения.

Верификация компонентов

Главная страница: Подробнее о компонентах и библиотеках

Ключевым аспектом верификации проекта является проверка корректности компонентов. Как правило, это осуществляется при добавлении компонентов в библиотеки предприятия. Типовые ошибки в компонентах, которые вызывают ошибки на плате, включают в себя:

- Некорректная ссылка на посадочное место – компонент ссылается на недоступное посадочное место. В процессе передачи проекта из редактора схем в редактор плат система ищет посадочное место в панели Components, в соответствии с настройками библиотеки, заданных для каждого посадочного места в диалоговом окне PCB Model.

- Выводы не соответствуют контактным площадкам – номера выводов символа компонента не соответствуют номерам контактных площадок. Система предполагает однозначное отображение: например, вывод 4 схемного символа соответствует контактной площадке 4 посадочного места. Это не обязательно – если номера не соответствуют друг другу, соответствие выводов и посадочных мест должно быть задано в процессе создания компонента в диалоговом окне PCB Model.

Прочие нарушения в компонентах, которые могут вызвать ошибки в проектах, включают в себя:

- Некорректное позиционное обозначение по умолчанию.

- Некорректное определение схемного вывода, например, его электрического типа.

- Потерянная проектная информация, такая как характеристики компонента, номер компонента, ссылка на даташит и т.д.

- Некорректно заданные скрытые выводы питания. В многосекционных компонентах их следует назначать нулевой логической ячейке, чтобы обеспечить их наличие независимо от того, какие ячейки компонента размещены на схеме.

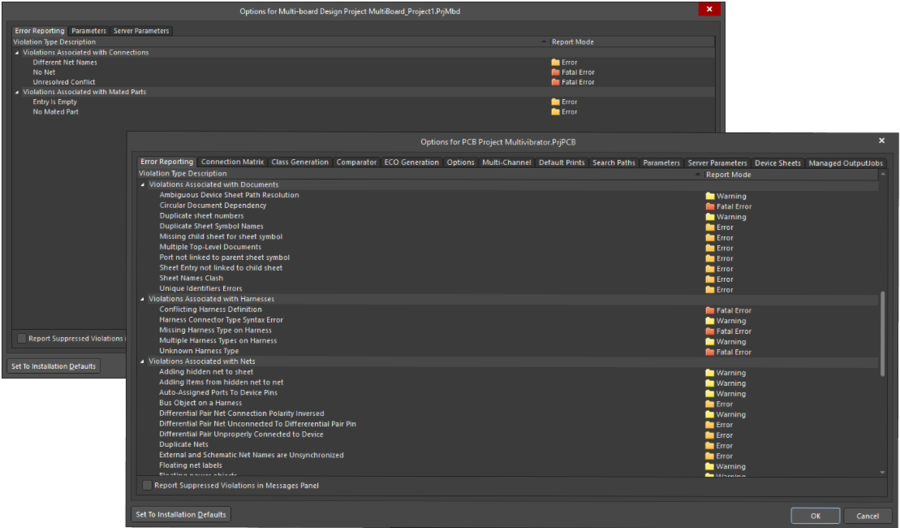

Настройка верификации

Главная страница: Диалоговое окно Project Options

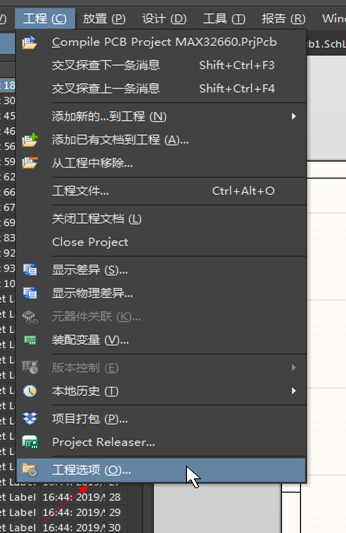

Существует обширный ряд графических и электрических проверок, которые можно осуществить для компилируемого проекта. Эти проверки настраиваются в параметрах проекта. Выберите команду Project » Project Options, чтобы открыть диалоговое окно Project Options (последовательность клавиш: C, O). Настройки по умолчанию не подойдут для всех проектов, поэтому важно ознакомиться с ними и понять, как их задавать в соответствии с вашим проектом.

Графические проверки

В ходе компиляции, общие ошибки графики и редактирования проверяются в соответствии с настройками на вкладке Error Reporting диалогового окна Project Options.

Настройка требуемых проверок.

Проверки сгруппированы по категориям, например Violations Associated with Nets (Нарушения, связанные с цепями), Violations Associated with Documents (Нарушения, связанные с документами), Violations Associated with Components (Нарушения, связанные с компонентами) и т.д. Группы представлены в списке в алфавитном порядке.

Режим отчета для каждого нарушения задан в столбце Report Mode, и для него можно выбрать одно из четырех значений, щелкнув по нему и выбрав нужный вариант из выпадающего списка: Fatal Error (Критическая ошибка), Error (Ошибка), Warning (Предупреждение), No Report (Без отчета).

Как правило, лучше сначала скомпилировать проект и проверить предупреждения в соответствии с настройками по умолчанию. Для тех предупреждений, которые не являются проблемой для данного проекта, уровень отчета можно изменить.

Одной из важных настроек является Nets with only one pin (Цепи только с одним выводом). Ее можно использовать для поиска цепей только с одним узлом, где вывод соединен с портом или меткой цепи, но не соединен с другим выводом. По умолчанию для этого нарушения не задан отчет, но его можно изменить на предупреждение для обнаружения таких цепей.

Проверки связности

Проверка электрической связности осуществляется в соответствии с настройками на вкладке Connection Matrix диалогового окна Project Options.

Матрица соединений определяет допустимые и недопустимые электрические состояния.

Матрица предоставляет механизм определения правил соединения между выводами компонентов и идентификаторами цепей, такими как порты и входы в лист. Она определяет логические и электрические состояния, о которых следует сообщать в виде предупреждений и ошибок. Например, выходной вывод, подключенный к другому выходному выводу, как правило, является ошибочным состоянием, в то время как соединение двух пассивных выводов – это нормальная ситуация.

Щелкайте по маленькому квадрату в матрице для изменения определенного правила. Каждое правило определяет уровень отчета для данного сочетания выводов/идентификаторов цепей. Для каждого правила существует четыре возможных значения: Fatal Error (Критическая ошибка), Error (Ошибка), Warning (Предупреждение), No Report (Без отчета).

Настройки на вкладках Error Reporting и Connection Matrix должны быть заданы в соответствии с требованиями текущего проекта.

Осмысление сообщений и поиск ошибок

Главная страница: Панель Messages

После компиляции проекта все предупреждения и ошибки приводятся в панели Messages. Обратите внимание, что панель Messages открывается автоматически, только если существуют ошибки. Чтобы проверить предупреждения, необходимо открыть панель. Нажмите кнопку Panels в нижней правой части приложения, чтобы открыть панель Messages. После того, как проект скомпилирован, в панели будут перечислены все найденные ошибки и предупреждения.

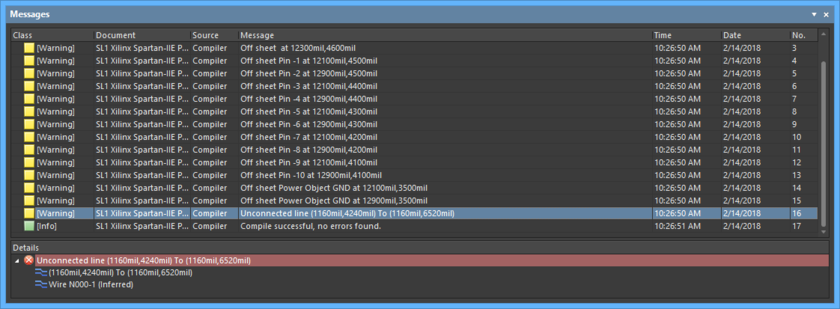

Панель Messages отображает найденные в проекте предупреждения и ошибки.

Панель Messages является центром управления, где отображаются нарушения компиляции. Следует иметь в виду следующее:

- Nets with no driving source (Цепи без источника возбуждения, категория Violations associated with Nets) – если цепь не содержит вывод с электрическим типом Output или I/O, возникает эта ошибка. Это может произойти и в корректных состояниях, например, если цепь соединяет вывод соединителя со входным выводом.

- Nets with multiple names (Цепи со множеством имен, категория Violations associated with Nets) – эта ошибка возникает, если вы изменяете имя цепи. Например, вы подключаете проименованную цепь ко входу в лист с другим именем (что допустимо), поскольку это имя входа в лист лучше отражает функцию цепи на листе более низкого уровня иерархии. Это также происходит в многоканальных проектах, где система должна назначить уникальное имя каждой повторяемой цепи.

- Component Revision has Inapplicable State (Ревизия компонента в неприменимом состоянии, категория Violations associated with Components) – при этой проверке появляется сообщение

Can't perform revision state validation(Невозможно провести валидацию состояния ревизии). Это нарушение возникает, когда ревизия компонента, размещенного с сервера управляемых данных, находится в неприменимом состоянии. - Панель Messages разделена на две области – в верхней части представлена таблица всех предупреждений/ошибок, в нижней – описание выбранного в данный момент предупреждения/ошибки.

- Дважды щелкните по сообщению, чтобы перейти к этому предупреждению/ошибке. Дважды щелкните мышью по описанию, чтобы отобразить конкретный объект.

- Вы можете щелкнуть по заголовку столбца в панели Messages (например, Class, Document, Message), чтобы отсортировать ошибки и предупреждения.

- Щелкните ПКМ в панели Messages и выберите команду Clear, чтобы очистить сообщения, или Export, чтобы экспортировать их в отчет.

- Панель включает в себя предупреждения и ошибки, обнаруженные в соответствии с настройками на вкладках Error Reporting и Connection Matrix.

- Чтобы открыть диалоговое окно Place Specific No ERC, нажмите кнопку

в панели инструментов Wiring. В диалоговом окне представлен список текущих предупреждений/ошибок компиляции. Здесь поддерживается переход к ошибке и размещение предварительно настроенной специфичной директивы No ERC для выбранной ошибки.

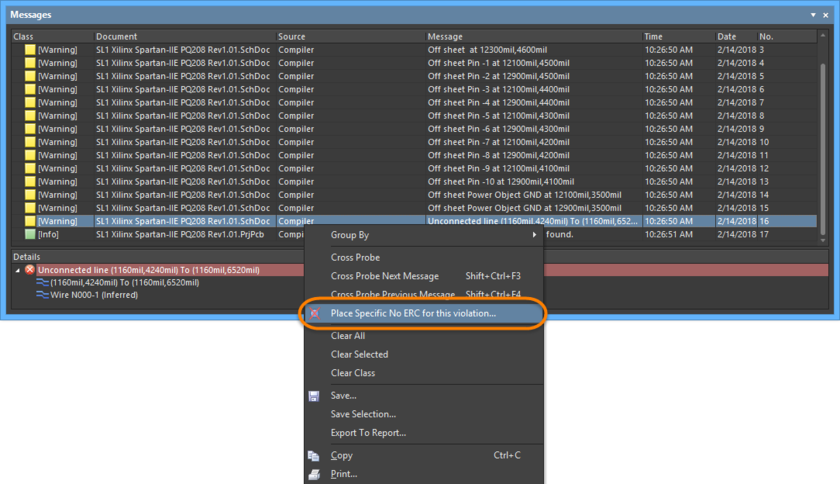

- При щелчке ПКМ по предупреждению/ошибке в панели Messages и выборе команды Place Specific No ERC for this violation вы автоматически перейдете к месту ошибки, и под курсором появится директива No ERC, готовая к размещению в месте ошибки. Нажмите клавишу Tab, чтобы отредактировать свойства директивы перед ее размещением, если необходимо.

- Общая директива подавит все проверки ошибок в точке своего размещения.

- Специфичная директива подавит только заданные проверки в точке своего размещения.

Исправление предупреждений и ошибок

Важно обращать внимание на все обнаруженные предупреждения и ошибки. Не все отчеты, заданные в настройках по умолчанию, могут быть проблемой на самом деле, но вы можете самостоятельно смягчить условия проверок. Например, в проекте может понадобиться, чтобы выводы входа-выхода были подключены ко входным портам, и для этого нужно настроить соответствующую ячейку на вкладке Connection Matrix. Другой проверкой, которую, как правило, нужно изменить, является Net has no driving source (Цепи без источника возбуждения), которую следует отключить на вкладке Error Reporting.

Могут быть ситуации, когда вам необходимо проверить весь проект на определенное условие, но вы хотите проигнорировать предупреждение/ошибку в определенном месте схемы. Например, вы хотите, чтобы цепь была переименована в определенном месте, но только в этом месте. Это можно сделать, разместив в этом месте директиву No ERC.

Использование директивы No ERC

Главная страница: Объект No ERC

Если необходимо, чтобы определенная точка схемы не формировала ошибку, разместите директиву No ERC (Electrical Rules Check – Проверка электрических правил) на этой точке (Place » Directives » Generic No ERC), что будет означать: «не помечать это место как предупреждение/ошибку«. Настройте стиль и цвет символа No ERC в соответствии с его предназначением на схеме в режиме No ERC панели Properties.

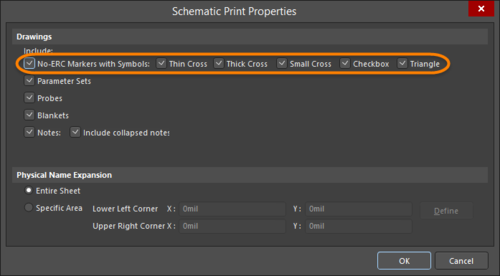

Обратите внимание, что директивы No ERC можно исключить из распечаток, если необходимо, включив соответствующие параметры в диалоговом окне Schematic Print Properties.

Вы можете разместить директиву Specific No ERC непосредственно в месте ошибки из панели Messages (щелкните ПКМ и выберите команду Place Specific No ERC for this violation, как показано на изображении ниже) или на нарушении.

Команда контекстного меню позволяет легко разместить специфическую директиву No ERC непосредственно в месте ошибки либо из панели Messages, либо из нарушения.

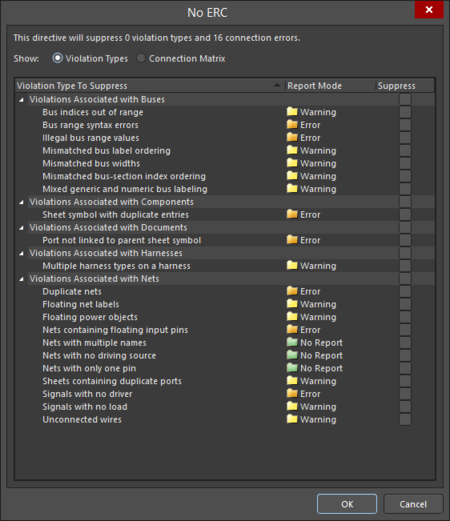

Обратите внимание, что директивы No ERC нельзя использовать для подавления всех типов проверок. Когда диалоговое окно No ERC находится в состоянии Violation Types, в нем отображен список типов нарушений, которые можно подавить. Используйте его для изучения того, какие проверки можно подавить.

Подробнее об ошибках компилятора

Система может проверять большое количество состояний потенциальных ошибок. Информация о каждой проверке доступна в Справочнике по нарушениям компиляции проекта.

Заключительным

этапом разработки схемы является

компиляция проекта. В процессе компиляции

окончательно выстраивается логическая

структура проекта. Выявляются ошибки,

допущенные при составлении электрической

принципиальной схемы.

Для

простого одноуровневого проекта, с

несложной однолистовой схемой, может

оказаться достаточным визуальный

контроль в ходе и по окончании формирования

документа. В сложном иерархическом

проекте ошибки могут ускользнуть от

визуального контроля. Чтобы этого не

происходило, в Altium Designer заложена развитая

система контроля ошибок.

Перед

компиляцией следует выполнить настройки

функций контроля. Настройки выполняются

в диалоге, активизируемом командой

главного меню Project>>Document

Options. Открывается

диалоговое окно Options

for Project<имя

проекта>.PrjPcb с десятью панелями-вкладками,

на которых перечислены все возможные

признаки, по которым выявляются ошибки

проекта.

В

плане компиляции, нас больше всего могут

интересовать настройки, призванные

выявить нарушения правил соединения

компонентов линиями электрической

связи и соответствие обозначений цепей,

портов, соединителей листов, в случае

многолистового проекта.

На

вкладке Error Reporting назначается характер

реакции программы на обнаруженные

нарушения:

• No

Report – не включать обнаруженное нарушение

в отчет;

•

Warning – вывести

предупреждение;

•

Error – вывести

сообщение об ошибке;

•

Fatal Error – вывести

сообщение о фатальной ошибке, при которой

невозможно выполнение операции.

Чтобы

установить уровень всех нарушений в

значение Error следует

нажать правой кнопкой мыши в любом месте

окна и выбрать All Error.

Все

типы нарушений на вкладке Error

Reporting разбиты на группы,

по отношению к определенному типу

объектов, варианты их отображения и

рекомендуемые настройки:

1.

Violations Associated

with Buses —

предупреждения, связанные с шинами.

2.

Violations Associated

with Components –

предупреждения, связанные с компонентами.

3.

Violations Associated

with Configuration

Constrains – предупреждения,

связанные с ограничениями конфигурации.

4.

Violations Associated

with Documents –

предупреждения, связанные с документами.

5.

Violations Associated

with Harnesses –

предупреждения, связанные со жгутами.

6.

Violations Associated

with Nets –

предупреждения, связанные с цепями.

7.

Violations Associated with Others, Violations Associated with

Parameters – предупреждения,

связанные с

параметрами и

другие.

На

вкладке Connection Matrix определяются правила

проверки электрических соединений

схемы, и назначается уровень реакции

программы на различные виды ошибок –

такие как соединение выхода с выходом,

выхода с питанием, двунаправленного

вывода компонента с выходным и т.п. На

пересечении столбцов и строк матрицы

стоят цветные метки, обозначающие

реакцию программы на соответствующее

соединение, обнаруженное при проверке

схемы. Выбирая соответствующую метку,

можем назначить один из четырех уровней

реакции – отсутствие реакции (если нет

ошибки), предупреждение, сообщение об

ошибке, фатальная ошибка. Каждому уровню

соответствует свой цвет – от зеленого

до красного.

Вкладка

Class Generation

– правила формирования классов цепей

и компонентов. При желании можно отключить

формирование комнат и классов компонентов

согласно подлистам схемы.

На

вкладке Comparator настраиваются правила

проверки соответствия имен одинаковых

объектов, цепей на листах многолистового

проекта и целого ряда других возможных

ошибок.

Вкладка

ECO Generation –

настройки отчета о перечне изменений.

Выбираются те изменения, которые следует

включить в отчет; по умолчанию включены

все опции – изменять эти данные

нецелесообразно.

Вкладка

Options – группа дополнительных

настроек проекта. Здесь задаются

директории сохранения отчета о компиляции,

компарации и т.д. В группе Output

Options выбираются действия,

которые следует применить после

выполнения процесса компиляции.

Вкладка

Multi Channel –

задает порядок номерации компонентов

при реализации многоканальных и

иерархических проектов.

Вкладка

Default Prints –

настройки распечатки документации

проекта.

Вкладка

Search Puths –

расположение библиотек, в которых по

умолчанию будет проводиться поиск

компонентов.

Вкладка

Parameters – параметры проекта,

которые могут быть использованы для

составления текстовых надписей,

являющихся общими для всех документов

проекта.

Вкладка

Device Sheets –

расположение директорий, содержащих

схемы, которые используются в проекте

в качестве готовых решений (подсхем) в

иерархии нижних уровней.

Компиляция

проекта выполняется по команде главного

меню Project>> Compile Document <имя_схемы>.SchDoc.

Если при компиляции обнаружены ошибки,

сообщения об ошибках выводятся на панель

Messages. В этом случае следует проанализировать

сообщения, внести в схемный документ

необходимые изменения и повторить

компиляцию проекта. Схемный документ,

откомпилированный без ошибок, может

быть передан на проектирование печатной

платы.

Соседние файлы в предмете [НЕСОРТИРОВАННОЕ]

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

- #

Altium Designer обеспечивает гибкую среду для установки различных правил проектирования, что обеспечивает целостность проекта. Обычно, правила проектирования устанавливаются в начале работы, а затем проводится проверка соответствия проекта правилам при компиляции.

Часто правила изменяются или добавляются новые во время трассировки. Для проверки платы на предмет соответствия установленным правилам проектирования после трассировки, используется программа DRC (Design Rule Check -Контроль Правил Проектирования). Программа Design Rule Checker (DRC) представляет собой высокопроизводительный автоматизированный программный модуль, проверяющий как логическую, так и физическую целостность проекта печатной платы. Использование этого модуля при трассировке обязательно для контроля соблюдения минимальных зазоров и отсутствия других нарушений. Так как редактор печатных плат позволяет в любое время вносить изменения в проект, рекомендуется всегда выполнять проверку правил проектирования перед окончательным выводом чертежей.

Функция проверки правил проектирования в режиме реального времени активизируется на вкладке PCB > General диалогового окна Preferences (см.Рис.1).

Рис.1. Включение функции проверки правил в режиме реального времени

Включение этой функции в режиме ручной трассировки позволяет незамедлительно обнаружить и выделить ошибки. Для установки правил которые будут поверятся в реальном времени необходимо выполнить Tools > Design Rule Checkи перейти на вкладку Rule To Check (см.Рис.2).

Рис.2. Список правил постоянной и ручной проверки

Для включения правила в постоянную (online) или ручную (batch) проверку следует установить флаг в соответствующем столбце напротив данного правила (см. Рис. 2).

Чтобы включить/выключить все правила, следует нажать ПКМ на названии любого правила и в выпадающем списке выбрать соответствующее значение. Рекомендуется для постоянной проверки выключить все правила (OnlineDRC—AllOff) и включить только проверку зазоров по металлизации и между компонентами (Clearance и Component Clearance). В ручную проверку желательно включить все правила, которые были созданы для данного проекта (Batch DRC-Used On).

Перед запуском ручной проверки можно указать дополнительные параметры на вкладке Report Options, которые позволяют:

- Create Report File – автоматически создавать файл отчёта программы проверки правил проектирования с расширением .DRC, который затем открывается текстовым редактором;

- Create Violations – подсвечивать нарушения; при включении этой настройки места нарушения правил (примитивы) будут выделяться заданным цветом;

- Sub-Net Details – работать совместно с правилом проектирования Unrouted Net Rule. Включается в случаях, когда требуется просмотреть все детали неразведённых цепей. Правило проектирования Unrouted Net Rule должно включаться только после трассировки всех соединений, т.к. виртуальная линия связи соединений воспринимается программой проверки как разомкнутая цепь;

- Verifyshortingcopper – проверка короткого замыкания;

- ReportDrilledSMDpads – автоматически создавать файл отчёта о сверлении SMDконтактных площадок;

- Reportmultilayerpadswith 0 sizehole — автоматически создавать файл отчёта о прокладки «нулевых» отверстий в многослойных платах;

- StopWhenXXViolationsfound– автоматически остановить процесс проверки правил проектирования при нахождении заданного числа нарушений.

Для запуска ручной проверки необходимо нажать кнопку Run Design Rule Check. Будетзапущен DRC иоткрытфайлотчёта Design Rule Verification Report. Результат всех обнаруженных в проекте нарушений будет отображён в панели Messages. Для перехода к ошибке на плате необходимо дважды нажать ЛК на ошибке в панели Messages. Места ошибок отмечаются стрелками и указывается невыполненный предел правила (если это касается правила зазора, см. Рис.3).

Рис.3. Обозначение ошибки правила зазора

Ремонт схема на PCB, прежде чем вам нужно будет компилировать схему и проверку электроэнергии, вы можете проверить схему с использованием функции ERC AD.

Схематическая компиляция:

Схематический интерфейс Выберите строку меню: Project —-> Compile PCB Project

Затем вы можете нажать на панели —-> Сообщение в правом нижнем углу, вы можете открыть интерфейс сообщений.

Для работы схема успешна, и пользователю необходимо изменить письмо об ошибке панели сообщения (модификация означает изменение вашей схемы), знать коррекцию завершения схемы

Обычное обнаружение схемы:

Схематический выбор меню выбора интерфейса: проект —-> Инженерные варианты

После нажатия, мы можем увидеть соответствующую информацию, все варианты, связанные с проектом, установит его в поле.

СПЕЦИАЛЬНОЕ ПРИМЕЧАНИЕ. Пользователи не хотят модифицировать систему Check Check = Формат отчета пункта, если пользователь не знает этих тестовых элементов

Наконец, слушать общие схематические ошибки

1, Дублируйте дизайнеры деталей: есть повторяющийся компонентный битовый номер

2, плавающие чистые этикетки: сетевая подвеска

3, Объекты с плавающей напряжением: есть парящий порт источника питания

4, сети с лишь контактом: есть односторонняя сеть

5, сеть с нескольким именем: имя сети повторить

6, Off Grid Object: объект не находится в растровой точке

Cистема проектирования Altium Designer 6. Часть 2.

Владимир Пранович,

[email protected]

(Оригинал статьи опубликован в журнале

Технологии в Электронной

Промышленности)

Параметры проекта

Перед передачей данных в PCB-проект желательно задать параметры проекта в

целом, так как от этого зависят условия передачи данных. Командой

Project\Project Option открываем окно параметров проекта. Мы оставим все

установки заданными по умолчанию. Однако, чувствуя себя опытным пользователем,

вы можете их установить по вашим требованиям. Те изменения, которые нужно будет

делать при создании сложных проектов, будут указаны в соответствующих

разделах.

На вкладке Error Reporting можно задать проведение контроля на

соответствующие поля и степень ошибки. Число параметров, по которым проводится

проверка, очень велико, и не имеет смысла их здесь приводить. В любом случае

помните, что лучший контролер — это вы сами.

На вкладке Connection Matrix аналогично задается проверка схем на

целостность сигналов.

На вкладках Class Generation задаются методы образования классов NET и ROOM

для компонентов на PCB.

На вкладке Comparator задаются правила нахождения различий между схемой и

PCB.

На вкладке ECO Generator можно включить или отключить формирование ECO для

отдельных классов отличий.

На вкладке Option задаются порядок хранения документов проекта, правила

связи иерархических схем, а также функции SWAP.

На вкладке Multi-Channel задается порядок имен NET и позиционных номеров для

иерархических и сложных схем.

Вкладка Default Prints — вид документов и их наполнение при формировании

отчетов и выходных файлов. Удобная вещь: когда вы подготовите уже не один

документ, то сможете быстро формировать выходные файлы. Это же касается и

вкладки Search Patch.

На вкладке Parameters зададим параметры, общие для всех листов проекта.

Например, таким параметром является номер разработки Dec_N =

EXAP.EXAMPLE.000.01 Э3. Для PCB нужна только общая часть Dec_N, и для нее

вводим параметр Dec_N = EXAP.EXAMPLE.001.01. Для того чтобы общая часть

передавалась в схему, проверьте, чтобы у конкретного листа схемы не был

прописан собственный параметр Dec_N. Как правило, его забывают удалить при

создании TITLE, и он кочует из схемы в схему. Если он есть, его следует

удалить.

PCB редактор

(TU0117 Getting Started with PCB Design)

Добавим к проекту новый PCB-документ и сразу сохраним его под именем

Example. В начале создадим заготовку проекта, которая в дальнейшем может

служить Template при создании новых PCB-проектов.

Создание рамки

Создадим в слое, например, Mechanical16 рамку, идентичными методами, как и

для схемы. Учтите, общие названия с рамкой из схемы могут быть автоматически

переданы из проекта через его параметры. Для этого при вставке текста перед

параметром ставится точка (рис. 14). Для задания рабочего поля (на весь размер

выбранного нами листа) используйте команду Design\Board Shape\Redefine Board

Shape. После этого его можно сохранить в качестве Template в соответствующую

папку.

Рис. 14. Пример заполнения полей при оформлении титульного листа

Передача данных между схемой и PCB и создание простых

проектов

Передача данных из схемного редактора в PCB производится командой

Design\Update PCB…. Эта команда идентична импорту данных в редакторе PCB из

Design\Import Change … из исходного проекта (рис. 15). Для передачи изменений,

сделанных в PCB-редакторе в схемный редактор, используется команда Design\

Update Schematic …. Пока нам понадобятся только первые две.

Рис. 15. Связь между компонентами схем проекта и PCB

Связь между компонентами схем проекта и PCB производится по уникальным

номерам. В результате многократных изменений в схеме или PCB, связь между

проектами может быть нарушена. Для изменения задания связи между компонентами

схемы и PCB при активном PCB-документе используется команда Project\Component

Link…. В первых двух колонках указаны компоненты схемы и PCB, связь между

которыми не установлена, справа — связанные компоненты. Вы легко можете

устранить связь, ввести ее вручную или автоматически, указав критерии связи по

параметрам (Designator, Comment, Footprint).

Следует всегда следить за однозначностью связи, но при любой передаче

данных, если отсутствует такая связь, всегда будет выдано предупреждающее

сообщение.

Из схемы в PCB-проект всегда передаются параметры Designator, Comment.

Установив для параметра Comment значение, например, =ValueSCH, можно передать

соответствующий параметр. Для желающих иметь одновременно не один, а несколько

параметров компонента в PCB-проекте, при создании Footprint следовало добавить

текст, например, .Designator или .Comment указав слой и параметры шрифта.

Однако рекомендуем этот прием использовать только чувствуя себя уверенным

пользователем. Тем более, что большой необходимости в этом нет.

Контур будущей платы задается линиями и окружностями в одном из слоев

Mechanical, область, доступная для разводки в слое Keep Out. Если они

совпадают, можно ограничиться последним. Начнем с простого прямоугольного

контура. Переключение между слоями производится нажатием «*» на дополнительной

клавиатуре или нажатием на закладку соответствующего слоя. Если вы этого слоя

не видите, включите его из окна «Контекстное меню \Option\Board layer &

colors…» (рис. 16). Здесь же вы можете настроить цвета, добавить слои и т. п.

После создания контура платы следует всем элементам контура установить свойство

Locked, чтобы избежать случайных перемещений элементов контура.

Рис. 16. Вид окна Board layer & colors…

Перейдем теперь к компонентам. У нас платка маленькая. В ней образована одна

Room под именем Example_1, совпадающим с именем листа схемы, так как мы

использовали установки по умолчанию. Чтобы поместить/удалить компоненты внутрь

Room, используйте команды Tools\Component Placement\Arrange Components Within

Room, …\Arrange Components Outside Board. Перемещая Room, мы перемешаем и все

компоненты. Нам проще переместить и изменить формы Room по размерам будущей

платы, сделать для Room опцию Room Locked, а затем переместить все компоненты

внутрь Room. После этого у нас все элементы стоят, как на рис. 17. Для

пользователей, знакомых с любой системой проектирования плат, не составит труда

получить и конечный продукт разводки.

Рис. 17. Начальное расположение элементов на Board

Отметим только ряд действий, которые придется совершить:

1. Установленный по умолчанию параметр Clearance имеет значение 0,254 мм.

Это не позволит провести дорожки, например, к контактным площадкам корпуса MSOP

(RM-8) MO-187AA. Для изменений этого параметра используется команда

Design\Rules:Electrical+Clearance, где наглядно устанавливается данный

параметр. Делаем его значение равным 0,2 мм. Здесь сразу же можете ознакомиться

с большим числом правил при проектировании плат. Определить их значения и есть

одно из главных действий для опытных пользователей.

2. Аналогично устанавливаем параметр Design\Rules:Routing+Width (минимальное

значение — 0,15 мм, по умолчанию — 0,25 мм, максимальное — 0,5 мм).

Будем считать процесс создания трассировки завершенным (рис. 18).

Рис. 18. Пример разводки

Наиболее часто используемый способ при проектировании — это возможность

установки на плату одного из нескольких вариантов корпуса компонента. При этом

речь не идет о выборе одного из вариантов корпуса (этот вопрос легко решаем и

не вызывает затруднений), а о соответствии компонента сложному посадочному

месту, включающему одновременно несколько вариантов исполнения корпуса,

например для SMD элементов корпуса типоразмеров 0805 и 1206, для транзисторов —

совмещение корпусов SOT23, SOT223, DPACK, для микросхем — SOIC и DIP.

Остановимся на создании составного корпуса для микросхемы LM5008, включающего

две разновидности MSOP8 и LLP8.

Вернемся в редактор PCB Library (TU0103 Creating Library Components) и

дополнительно к существующему посадочному месту MSOP8, которое мы уже

использовали, создадим LLP8. Затем создадим совмещенный корпус MSOP8_LLP8

копированием в него изображений его составляющих. Заметьте, что новый корпус

будет содержать по два PAD c номером 1, по два PAD c номером 2 и так далее. В

слое Top Layer командой Place\Line соединяем PAD с одинаковыми номерами. Новый

компонент готов. Таким же образом можно задать сложную форму для контактной

площадки, положив сверху полигон. Но при использовании полигона, если требуется

освобождение его от маски, соответствующая графика должна быть прорисована

отдельно, так как для полигонов, в отличие от PAD, автоматической генерации ее

нет.

Теперь подключаем новый компонент в качестве текущего в схему (напрямую, или

введя соответствующие изменения в Schematic Library) и обновляем PCB-проект. К

сожалению, изображение данного составного корпуса не совсем информативно, так

как корпус LLP8 можно смонтировать на месте посадочного места MSOP8. Поэтому на

рис. 19 показано также и составное посадочное место SOT23_SOT223_DPACK. В

последнем примере PAD корпуса SOT23 выполнены полигонами и соединены линиями с

PAD корпуса DPACK; PAD корпуса SOT223 совмещены.

Рис. 19. Примеры составных посадочных мест

Подготовка документации и файлов для производства

Для подготовки документации в пакете имеется развитая система их

автоматического формирования. Рассмотрим только основные из них. Остальные

легко осваиваются по мере надобности.

Формирование файлов для производства печатных плат

Команда File\Fabrication Output\Gerber Files используется для создания

Gerber файлов.

— В окне General задаем размерность и формат формируемых файлов.

— В окне Layers задаем слои, для которых формируются выходные данные. В

нашем случае (считаем, что плата однослойная) это:

– Top Layer — верхний слой;

– Top Overlay — верхний слой шелкографии (надписей);

– Keep Out Layer — контур обрезки.

— В окне Drill Drawing происходит задание отображения символов сверловки. Мы

будем формировать файл сверловки отдельно.

Поэтому можно их не задавать.

— В окне Apertures — задание апертур. Ставим галочку RS274X.

— В окне Advance — размеры фотошаблонов. Оставляем по умолчанию.

При оформлении документации можно прикрепить к формируемым Gerber Files

дополнительный слой, скажем, с нашей рамкой, выполненной по ГОСТу.

Команда File\Fabrication Output\\NC Drill Files используется для

формирования файла сверловки.

Формирование сборочного и монтажного чертежа

Команда File\Assembly используется при формировании вспомогательных файлов

для удобства монтажа печатных плат. Предварительно все слои и тип выводимой

информации задаются в окне Project\ProjectOption\ Default Prints:Assembly

Output: Assembly Drawing. Здесь же можно задать и вывести на печать большое

количество созданных вами заготовок для документов.

Рассмотрим подробнее дополнительные изменения в PCB-проекте для удобства

дальнейшей работы и соответствия требованиям технологических чертежей.

Для подготовки сборочного чертежа для монтажного участка расположение и

распечатка позиционных обозначений элементов, используемых в слое Top Layer, не

совсем удобна. Во-первых, надписи в этом слое могут иметь малый размер и при

выводе на печать, во-вторых, при плотном монтаже они вообще могут не насены на

чертеж или плату, и в-третьих, что самое принципиальное, они могут иметь не

адекватное прочтение, что вызывает некорректную сборку печатной платы. Эту

проблему можно решить двумя способами:

— Первый. В редакторе PCB выделим все компоненты и установим свойства для

параметра Designator — размещение (autoposition) в центре и нужный слой — и

дальше готовим вариант для печати. Это самый простой и очевидный способ, но у

него есть несколько недостатков. Во-первых, необходимо делать «откат» от

произведенных действий, чтобы не изменить надписи в слое Top Layer (изображение

надписей на плате не должно меняться), а про это часто забывают. Во-вторых,

надписи для удобства чтения лучше сделать максимально большими — по размеру

корпуса компонента.

— Второй способ может показаться сложнее. Зато он в принципе позволяет

получать независимые изображения Designator для Top Layer и другого

технологического слоя, который и может использоваться при создании чертежей для

монтажного участка. Более того, таким же способом можно получить и другие

чертежи, например, с маркировкой элементов или их номиналами.

Для этого вернемся в редактор PCB Library (TU0103 Creating Library

Components).

Здесь для всех компонентов командой Place\String ввести на слой, который

будет использоваться при изготовлении чертежа для монтажного участка, например,

Mechanical 1, надпись .Designator и выбрать положение шрифта и его размер в

соответствии с конкретным корпусом. Будьте внимательны!

Именно точка в начале надписи означает, что данные будут передаваться из

схемы в PCB-проект. Затем все компоненты в PCB-проекте следует обновить

Tool\Update… в соответствии с измененной библиотекой и установить галочку

Convert Special String в установках PCB-редактора (DXP\Preferences\PCB

Editor\Display). Далее останется только провести редактирование тех надписей,

которым присвоены значения Designator, состоящие из длинных записей и не

вписывающиеся из-за этого в размер корпуса. При грамотном подходе эти надписи

править не нужно, и для того, чтобы они были закрыты по умолчанию, для

редактирования в свойстве надписи (в PCB Library) следует установить свойство

Locked. На рис. 20 приведены рисунки исходного вида чертежа части платы до и

после проведения указанных действий.

Рис. 20. Вывод Designator в дополнительном слое

Таким образом, можно из схемы в PCB-проект передавать и значения любых

других параметров, например, ранее введенный нами параметр MarkPCB (маркировку,

нанесенную на корпус элемента). Однако, здесь есть ограничение. Для этого при

создании посадочного места используется параметр Comment, а для передачи

значения другого параметра из схемы на PCB используется его переопределение

Comment=MarkPCB. Это удобно для поиска и определения типа смонтированных

компонентов, так как на малых по размеру корпусах наносят несколько символов,

по которым можно найти полное название элемента.

Формирование заготовки перечня элементов схемы и спецификации

сборочного чертежа

Для этого используется команда Reports\Bill of Materials. Она доступна и из

схемного редактора, и из редактора PCB. Типовые настройки показаны на рис. 21.

В колонку Grouped Columns из колонки All Columns переместите параметры, по

которым должно производиться группирование, при создании спецификации. В обеих

этих колонках отметьте галочками те параметры, которые будут присутствовать в

спецификации. В правом окошке перетаскиванием колонок создайте их порядок

следования в спецификации. Внизу укажите формат сохраняемого файла. Удобно

сразу подключить файл, содержащий заготовку спецификации. В этом случае вы

получите практически готовый перечень элементов или спецификацию. При

использовании EXCEL есть одно ограничение. Для больших проектов надписи,

например в колонке Designator, могут не поместиться в ячейку EXCEL, и тогда они

игнорируются. На рис. 21 выведены установки для стандартных колонок в перечне

элементов.

Рис. 21. Создание перечня элементов

Формирование полного пакета выходных данных

Так как описано выше, вы можете создать указанные документы для вашего

проекта. Однако каждый раз формировать и прописывать параметры формируемых

документов нет необходимости. Достаточно один раз настроить их для типовых

проектов и затем использовать как стандартные. Для этого введем в проект новый

документ Project\Add New to Project\Output Job File. В открывшемся документе вы

можете подготовить любые формируемые выходные файлы и их параметры, включая

различные модификации. В том числе для схем, поддерживающих наличие различных

элементов и номиналов, в зависимости от исполнения изделия. Один раз

прописанный файл типа Output Job File может быть легко скопирован или добавлен

к новому проекту, это дает существенное сокращение времени на подготовку

выходных файлов для каждого нового проекта.

Иерархические схемы

Перейдем к одному из принципиальных отличий Altium Designer 6 от PCAD200x —

это возможность построения иерархических схем и автоматический перенос

трассировки идентичных блоков в PCB-проекте.

Требования к иерархическому проекту и подготовка к его

созданию

Итак поставим себе задачу создать проект, включающий в себя 6 DC/DC

преобразователей, схема которых нами использовалась в предыдущем проекте, на

формирующие уровни питания: один на 3,3 В, четыре на 5,0 В и один на 10 В.

Как уже делали ранее, сформируем новый проект Example2. Хотя проект можно

перенести и обычным копированием. Единственное необязательное требование: дайте

всем файлам проекта и самому проекту другие имена, откройте его и добавьте к

новому проекту переименованные документы. Откроем пока единственный лист нашей

схемы и сохраним (перенесем) в новом проекте под именем Example_2_L2 и изменим

в свойствах проекта общие параметры …EXAMPLE.000.01 на …EXAMPLE.000.02.

Заменим Template с первого листа рамки ГОСТа на второй. Все это не

обязательные требования, а лишь следование требованиям ГОСТа.

Изменение схемы модуля

Изменим частично схему, заменив все Power Port на простые Net Label, так как

все изменения в иерархии вначале мы передадим через Port. Добавим ко всем

входным и выходным сигналам Port. После преобразований схема выглядит так, как

показано на рис. 22.

Рис. 22. Пример схемы

Все модули питания схематично будут выглядеть одинаково, за исключением

номиналов некоторых элементов схемы. На этом схему модуля можно считать

завершенной.

Создание типовых иерархических схем

Создадим в проекте новый первый лист схемы Example_2_L1. Воспользуемся

командой Design\Create Sheet Symbol From Sheet Or HDL. В открывшемся окне в

списке листов проекта появится единственный, отличный от этого лист схемы

Example_2_L2. Выбираем его и у нас появится на схеме Sheet Symbol. Изменяем

значение его Designator на A1 Подключаем лист к Sheet Entry, как показано на

рис. 23 и имеем законченную ссылку на модуль DC/DC для аналогового питания на

10 В.

Рис. 23. Пример Sheet Symbol

Переход в иерархии производится при нажатой клавише Ctrl на изображении

Sheet Symbol, обратно тоже, но по любому из Port. При этом оба документа должны

быть открыты. После этого проделайте операцию Project\Compile PCB Project, и

изображение в панели Project для схем проекта будет иметь вложенный

характер.

Однако это самый простой, правда, и наиболее распространенный способ

применения иерархических схем. Перейдем ко второму случаю — блоку питания на

3,3 В. Он ничем не отличается от первого, за исключением номиналов резисторов

R3 и R4. Ради этого нет смысла полностью перерисовывать схему. Осуществим

следующие действия (AR0112 Multi-Channel Design Concepts).

1. В уже имеющемся Sheet Symbol введем следующие параметры:V_Out=10V;

R3=3.01k; R4=1.0k, означающие, что для уровня 10 В номиналы резисторов R3 и R4

имеют указанные значения. Сделаем видимым как само имя параметров, так и его

значение.

Отредактируем Sheet Symbol.

2. Скопируем Sheet Symbol, изменим его параметры для условия формирования

выходного напряжения 3,3 В и добавим соответствующую обвязку.

3. Перейдем на нижний уровень и в параметрах ValueSCH для резисторов R3 и R4

введем значения, соответственно, =R3 и =R4 и сделаем их видимыми, а параметр

Comment невидимым. После чего следует провести компиляцию проекта, и значения

из верхней схемы иерархии передадутся в нижнюю. Параметр из Sheet Symbol

передается напрямую в указанный параметр конкретного компонента модуля, но

через него в Comment нет. Будем надеяться, что в ближайших релизах пакета это

будет устранено, что принципиально не меняет сущности этого подхода.

Переключаясь между модулями A1 и А2 листа Example_2_L2, вы наглядно видите

изменение номинала резистора R3, как и было задано.

Перейдем к введению в схему четырех идентичных модулей на 5 В. После

копирования и введения соответствующего параметра для резисторов R3 и R4 нужно

указать, что таких модулей у нас 4. Для этого в его Designator делаем запись

Repeat(A,3,6), где

— надпись Repeat означает повторяющийся модуль;

— в скобочках первый символ «А» — это и есть значение Designator для

модуля;

— 3,6 — первый и последний номер в повторяющейся серии.

Рис. 24. Пример схемы с несколькими одинаковыми модулями

Таким образом, мы создадим четыре идентичных модуля с позиционными номерами

A3, A4, A5, A6 (рис. 24). Заметим, что линии связи, подводимые к Sheet Entry с

именами In_Vcc (входной уровень питания) и GND («земля») являются общими, а

Shutdown (включение питания) и Vcc_Out (выходной уровень питания) в принципе

могут отличаться. На последнем и остановимся. Для этих сигналов в Sheet Entry

также нужно вписать Repeat(…). Соответственно скорректируем схему: для шинных

сигналов в квадратных скобочках указываем начальное и конечное значение сигнала

в шине. Так как мы сами формируем имена связей и одному Sheet Entry в нашей

схеме соответствуют разные связи, галочку Project\Project Option:Option-Allow

Sheet Enter to Name Net следует снять.

Мы сознательно остановимся на незавершенной схеме первого листа, так как

принцип иерархии она все равно отображает. В общем случае по завершении нужно

сделать операцию Annotate и Compile. При операции Annotate вы можете установить

порядок листов при присвоении позиционных номеров, но лучше сделать это при

помощи операции Tool\Number Sheets. При Compile у нас создались сообщения об

ошибках Floating Power Object. Мы их игнорируем, это связано с незавершенностью

схемы.

Связь иерархических проектов

(AR0123 Connectivity and Multi-Sheet Design)

Итак, мы видим, что работа с иерархическими проектами удобна не только при

создании схем, но и далее, при трассировке проекта в целом и блоков в

отдельности.

Работа в редакторе PCB

Создаем новую заготовку PCB и передаем данные из схемы в PCB. Для этого

используем команды Design\Update PCB… при активной схеме или Design\Import

Change…. При постоянном внесении изменений в схеме и PCB и для полного

согласования компонентов схемы и PCB следует поддерживать и отслеживать связь,

используя команду Project\Component Links, доступную при активном документе

PCB.

На PCB видим 6 Room. Берем любую из них и, как делали ранее, расставляем

компоненты и разводим связи. Делая эти операции, вы могли воспользоваться и

результатами предыдущей разводки в проекте Example. Однако сейчас на этом

останавливаться не будем. У нас на PCB Designator включает имя Room. Это, с

точки зрения автора, дает много ненужной информации, а главное — длинные

надписи сложно затем разместить на слое TopSilk. Переключение отображения между

физическими позиционными номерами (с включением дополнительной информации) и

логическими (только позиционные номера на соответствующем листе схемы модуля)

производится командой Design\Board Option.

Перемещаем одну из Room на поле, где и производим расстановку элементов и

создание топологии в Room. C остальными поступаем проще, а именно:

— выбираем команду Design\Room\Copy Room Format, мышкой отмечаем Room,

формат которого берется за основу, затем один из тех Room, куда нужно перенести

формат;

— устанавливаем все галочки в параметрах для копирования формата и все Room

(далее вы сможете переносить только формат расположения элементов или разводку,

указать конкретные Room для переноса формата).

После выполнения команды все Room приобрели одинаковый вид. Однако из-за

возможного большего размера нашей Room, может произойти наложение Room друг на

друга. Чтобы этого не произошло, необходимо побеспокоиться об этом заранее и

разнести Room вручную. Однако и сейчас это можно сделать в автоматическом

режиме:

— выделите все Room;

Рис. 25. Результат трассировки 6 идентичных модулей

— используя команду Design\Room\Arrange Room, расставьте выделенные Room в

выбранной вами последовательности. При этом перенесутся только те объекты,

которые находятся полностью внутри Room, а находящиеся за пределами (такое

может быть, если Room накладывались друг на друга) останутся на месте. В

последнем случае операцию …\Copy Room Format следует повторить, а остатки линий

удалить. Эти функции существенно сокращают процесс трассировки сложных плат с

идентичными блоками. В результате у нас получилась трассировка 6 идентичных

блоков (рис. 25). Нам остается вручную произвести трассировку только тех линий

связи, которые связывают между собой Room.

Окончание

следует

Литература

1. Пранович В. Система проектирования Altium Designer 6 // Технологии в

электронной промышленности. 2006. № 5.

Полный цикл

статей